Homework #1

Guidelines

- Complete your work on green engineering paper

- Staple in upper left if more than one sheet.

- Format the top of the first sheet as follows.

| CSCE 436 | [Your name] | HW#1 | [Due Date] | [Page ref]

|

The page reference for the first page of a four page document would be 1/4, the

second page of this document would be labeled 2/4 and so on.

- Do not write on the back side of the green engineering paper

- Digital copies of all code, testbenches, and waveforms will also be submitted via BitBucket.

- [1.2] Volume of sale (i.e., the number of parts sold) is a factor when

determining which device technology is to be used. Assume that a

system can be implemented by FPGA, gate array or standard-cell

technology. The per-part cost is $15, $3, and $1 for FPGA, gate array,

and standard cell respectively. Gate-array and standard-cell technologies

also involve a one-time mask generation cost of $20,000 and $100,000

respectively. Assume the number of parts sold is N. Derive the equation

of per-unit cost for the three technologies.

- Assume the number of parts sold is N. Derive the equation of per-unit cost for the three technologies.

- Plot the equations with N as the x-axis.

- Determine the range of N for which FPGA technology has the minimal per-unit cost.

- Determine the range of N for which gate-array technology has the minimal

per-unit cost.

- Determine the range of N for which standard-cell technology has the minimal

per-unit cost.

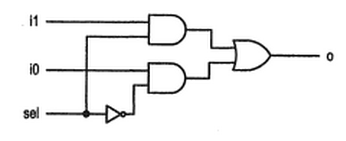

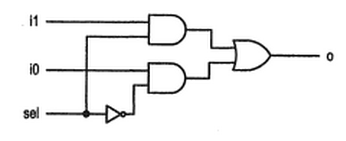

- [1.3] What is the view (behavioral, structural, or physical) of the following illustration?

- [1.4] What is abstraction? Why is it important for digital system design?

- [1.5] What is the difference between testing and verification?

- Install and test Xilinx Vivado: Vivado Installation Instructions

- Design a digital system with four bits of inputs I3 I2 I1 I0 and

two bits of outputs O1 O0. At least one of the inputs is always equal

to 1. The output encodes the index of the most significant 1 in the

input. For example, if I3 I2 I1 I0 = 0101, then the index of the most

significant 1 is 2, hence O1 O0 = 10. Hint, you will need a don't

care somewhere. Turn in....

- Complete truth table.

- Two 4-variable kmaps.

- Minimal SOP expressions for O1 and O0

- VHDL code for the circuit (attached as computer print-out and pushed to BitBucket).

Make sure that you have a proper file header.