# Getting Started with Vivado and Vitis for Baremetal Software Projects

# Overview

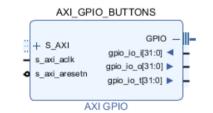

This guide will work you through the process of setting up a project in Vivado and Vitis. A simple hardware design including a processor with several AXI <u>GPIO ()</u> peripherals connected to buttons and LEDs will be created. This design will then be exported to the Vitis IDE, and a baremetal software project will be created and run which polls the buttons and writes to the LEDs.

Note: Screenshots presented in this guide may not have been taken with your version of the tools. The workflow presented here has been verified in Vivado and Vitis 2020.1.

## Inventory

- A Digilent FPGA Development Board

- USB Programming cables, USB UART cables, and Power Supply, as required by the board.

- · Vivado and Vitis installations

- See Installing Vivado, Vitis, and Digilent Board Files (https://digilent.com/reference/programmable-logic/guides/installing-vivado-and-vitis) for instructions on how to install these tools.

- You also need the board files for your board. This guide is intended for use with the board files available from Digilent's vivado-library repo on Github. You can get these files using the process described in the Installing Vivado, Vitis, and Digilent Board Files (https://digilent.com/reference/programmable-logic/guides/installing-vivado-and-vitis) guide. These files will also be available through the Vivado application itself in versions 2022.1 and newer.

Note: If you are using a version of Vivado that includes Xilinx SDK (2019.1 or older), check out Getting Started with Vivado IP Integrator and Xilinx SDK (https://digilent.com/reference/vivado/getting-started-with-ipi/2018.2).

# Guide

## Launch Vivado

Select the dropdown corresponding to your operating system, below.

## Windows

Open Vivado through the start menu or desktop shortcut created during the installation process.

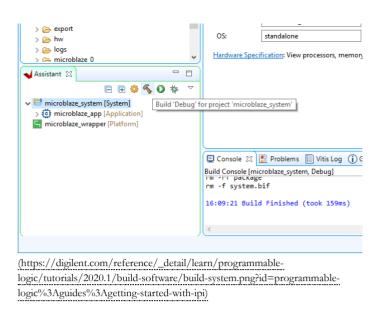

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/launch-vivado/open-vivado.png?id=programmablelogic%3Aguides%3Agetting-started-with-ipi)

## Linux

Open a terminal, and change directory (cd) to a folder where log files for your Vivado session can be placed, then run the following commands:

source <install\_path>/Vivado/<version>/settings64.sh

vivado

(https://digilent.com/reference/\_detail/vivado/getting\_started/linux\_start\_vivado. id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

## Create a Vivado Project

In Vivado's welcome screen, several options are presented:

- **Create Project:** Opens a wizard used to begin creating a Vivado project from scratch, which will be used here.

- **Open Project**: Can be used to open a Vivado project (defined by an XPR file) that has been previously created or downloaded from the internet.

- **Open Hardware Manager**: Can be used to program an FPGA development board with a bitstream, without opening the associated project.

Note: Various other options are available, but are not described here.

For the purposes of this guide, click the **Create Project** button.

logic/tutorials/2020.1/create-vivado-project/create\_project.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

The first page of the New Project wizard summarizes the steps involved in creating a project. Click **Next**.

| New Project  |                                                                                                                                                                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Create a New Vivado Project                                                                                                                                                                                                                 |

| HLx Editions | This wizard will guide you through the creation of a new project.                                                                                                                                                                           |

|              | To create a Vivado project you will need to provide a name and a location for your project files. Next, you will specify the type of flow you'll be working with. Finally, you will specify your project sources and choose a default part. |

|              |                                                                                                                                                                                                                                             |

|              |                                                                                                                                                                                                                                             |

|              |                                                                                                                                                                                                                                             |

|              |                                                                                                                                                                                                                                             |

|              |                                                                                                                                                                                                                                             |

|              |                                                                                                                                                                                                                                             |

|              |                                                                                                                                                                                                                                             |

| XILINX.      |                                                                                                                                                                                                                                             |

| ?)           | < Back Next> Einish Cancel                                                                                                                                                                                                                  |

logic/tutorials/2020.1/create-vivado-project/new-project-1.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

The first step is to set the *name* for the project. Vivado will use this name when generating its folder structure.

**Important:** Do NOT use spaces in the project name or location path. This will cause problems with Vivado. Instead use an underscore, a dash, or *CamelCase* (https://en.wikipedia.org/wiki/CamelCase).

Pick a memorable *location* in your filesystem to place the project.

Checking the **Create project subdirectory** box will create a new folder in the chosen location to store the project's files. This is recommended.

Click Next to continue.

| À New Project                      |                       |                          |                           |                |        | ×      |

|------------------------------------|-----------------------|--------------------------|---------------------------|----------------|--------|--------|

| Project Name<br>Enter a name for y | our project and speci | fy a directory where the | e project data files will | be stored.     |        | A      |

| Project name:                      | PmodIPs               |                          |                           |                |        | 8      |

| Project location                   | D:/Work/PmodIPs       |                          |                           |                |        | ⊗      |

| Create proje                       | ct subdirectory       |                          |                           |                |        |        |

| Project will be c                  | reated at: D:/Work/Pm | odIPs/PmodIPs            |                           |                |        |        |

|                                    |                       |                          |                           |                |        |        |

|                                    |                       |                          |                           |                |        |        |

|                                    |                       |                          |                           |                |        |        |

|                                    |                       |                          |                           |                |        |        |

|                                    |                       |                          |                           |                |        |        |

|                                    |                       |                          |                           |                |        |        |

|                                    |                       |                          |                           |                |        |        |

|                                    |                       |                          |                           |                |        |        |

|                                    |                       |                          |                           |                |        |        |

| ?                                  |                       |                          | < Back                    | <u>N</u> ext > | Einish | Cancel |

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/create-vivado-project/new-project-2.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

At the Select Project Type screen, choose **RTL Project** and check the *Do not specify sources at this time* box. Advanced users may want to use the other options on this screen, but they will not be covered here.

Click Next to continue.

| roje  | ect Type                                                                                                                                      |                                      |        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------|

| pecif | fy the type of project to create.                                                                                                             |                                      | 1      |

| ۲     | BTL Project<br>You will be able to add sources, create block designs in IP Integrator, gener<br>implementation, design planning and analysis. | ate IP, run RTL analysis, synthesis, |        |

|       | Do not specify sources at this time                                                                                                           |                                      |        |

| 0     | Post-synthesis Project<br>You will be able to add sources, view device resources, run design analysis<br>Do not specify sources at this time  | , planning and implementation.       |        |

| 0     | J/O Planning Project<br>Do not specify design sources. You will be able to view parl/package resour                                           | ces.                                 |        |

| 0     | Imported Project<br>Create a Vivado project from a Synplify, XST or ISE Project File.                                                         |                                      |        |

| 0     | Example Project<br>Create a new Vivado project from a predefined template.                                                                    |                                      |        |

|       |                                                                                                                                               |                                      |        |

|       |                                                                                                                                               |                                      |        |

|       |                                                                                                                                               |                                      |        |

| ?     | < Back                                                                                                                                        | Next > Einish                        | Cancel |

| tos   | s://digilent.com/reference/_detail/learn/p                                                                                                    | rogrammable-                         |        |

| ·^··· | /tutorials/2020.1/create-vivado-project/nev                                                                                                   | ¥                                    |        |

Next, a part or a board must be chosen for the project to target. The project will only be usable with the chosen device (though the selection can later be changed through the project's Settings).

Selecting a board over a part is recommended, as the board files provide additional configuration information for a variety of peripherals and components in a design. Click the **Board** button to open the board tab.

Search for your board and select it from the list.

**Important:** If your board does not appear in the list, Digilent's board files have not been installed. Review Installing Vivado, Vitis, and Digilent Board Files (https://digilent.com/reference/programmable-logic/guides/installing-vivado-and-vitis) for instructions on installation of these files.

Click Next to continue.

| Vew Project                                           |         |                |                 |             |

|-------------------------------------------------------|---------|----------------|-----------------|-------------|

| fault Part                                            |         |                |                 |             |

| oose a default Xilinx part or board for your project. |         |                |                 | . · · · · · |

|                                                       |         |                |                 |             |

| Parts   Boards                                        |         |                |                 |             |

| Reset All Filters                                     |         |                | Update Board Re | epositories |

| Vendor: All 🗸 Name: All                               |         | ~              | Board Rev. Late | est 🗸       |

| Search: Q- Zybo Z7-10 💿 🗸 (1                          | match)  |                |                 |             |

| Display Name                                          | Preview | Vendor         | File Versio     | n Part      |

| Zybo Z7-10                                            |         |                |                 |             |

|                                                       |         | digilentinc.co | m 1.0           | xc7z010(    |

|                                                       |         |                |                 |             |

|                                                       |         |                |                 |             |

|                                                       |         |                |                 |             |

|                                                       |         |                |                 |             |

|                                                       |         |                |                 |             |

| <                                                     |         |                |                 | >           |

|                                                       |         |                |                 |             |

|                                                       | < Back  | Next >         | Finish          | Cancel      |

| )                                                     |         |                |                 | Cancel      |

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/create-vivado-project/new-project-4.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

The last screen of the New Project wizard summarizes what was chosen in the previous screens. Click **Finish** to open your project.

| 🟊 New Project     | ×                                                                                                                                                                                                    |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | New Project Summary                                                                                                                                                                                  |

| HLX Editions      | A new RTL project named 'PmodiPs' will be created.                                                                                                                                                   |

|                   | The default part and product family for the new project:<br>Default Board. Zybo Z7-10<br>Default Part Xr230106400-1<br>Product. Zynq-7000<br>Family: Zynq-7000<br>Package: clg400<br>Speed Grade: -1 |

|                   |                                                                                                                                                                                                      |

|                   |                                                                                                                                                                                                      |

| E XILINX.         | To create the project, click Finish                                                                                                                                                                  |

| •                 | <back net=""> Einish Cancel</back>                                                                                                                                                                   |

| https://digilent. | com/reference/_detail/learn/programmable-                                                                                                                                                            |

| ogic/tutorials/20 | )20.1/create-vivado-project/new-project-5.png?                                                                                                                                                       |

| d=programmabl     | e-logic%3Aguides%3Agetting-started-with-ipi)                                                                                                                                                         |

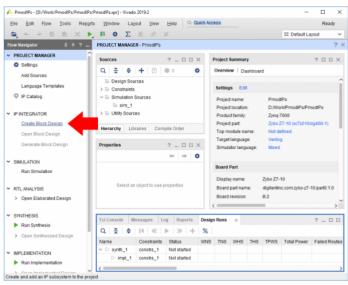

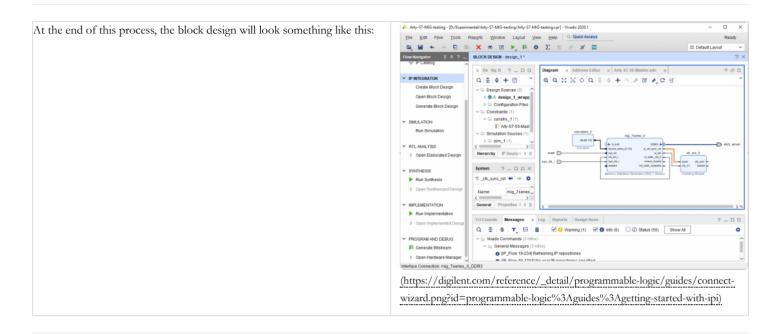

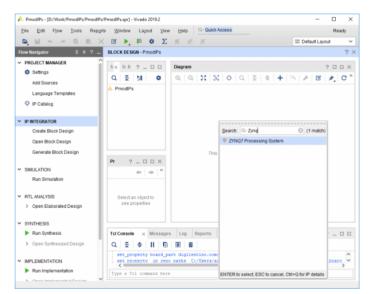

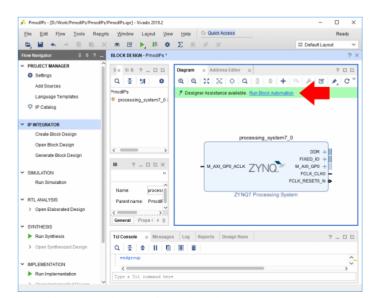

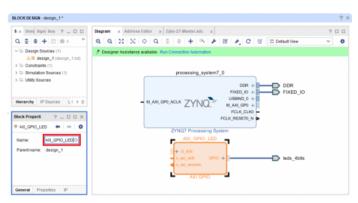

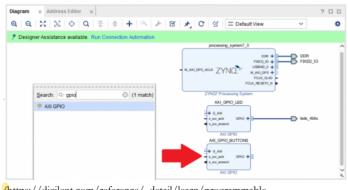

# Create a Block Design

Click the **Create Block Design** button in the *IP Integrator* dropdown of Vivado's *Flow Navigator* pane. A block design provides a visual representation of your hardware design, and can be used to easily connect and configure IP cores.

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/create-block-design/create-block-design-1.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

In the dialog that pops up, give your block design a name (or use the default "design\_1").

**Important:** Do NOT use spaces in the block design name. Instead use an underscore, a dash, or ③ CamelCase (https://en.wikipedia.org/wiki/CamelCase).

The other two fields should be left as defaults. *Directory* can be used to place the block design's source files outside of the project directory, and *Specify source set* can be used to create block designs that are not part of the normal Design Sources, which are used to build the project.

Click OK to continue.

| 🍌 Create Block Design |                                    | ×         |

|-----------------------|------------------------------------|-----------|

| Please specify name   | of block design.                   | A         |

| <u>D</u> esign name:  | PmodIPs                            | $\otimes$ |

| D <u>i</u> rectory:   | 😜 <local project="" to=""></local> | ~         |

| Specify source set:   | 🗅 Design Sources                   | ~         |

| ?                     | ок                                 | Cancel    |

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/create-block-design/create-block-design-2.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

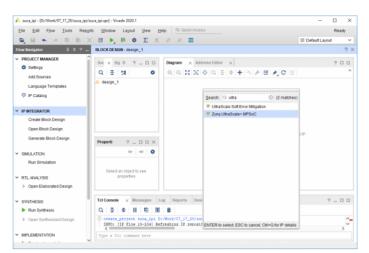

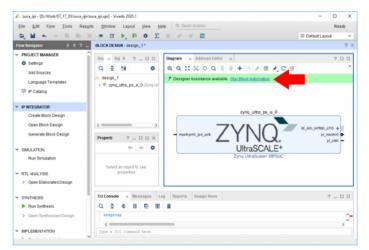

## Add a Processor to a Block Design

The process of adding a processor to your design is very different depending on the processor used. The Microblaze dropdown should be selected only if using a board that does not have a Zynq or Zynq UltraScale+ device.

#### Add a Microblaze Processor to a Block Design

The Microblaze soft-core processor IP can be used to instantiate a processor within your FPGA design. This processor can be very useful for controlling and configuring hardware components. This section discusses how you can add a Microblaze processor and several useful components, including UART for standard output and DDR memory support, to your block design.

Note: This section is intended for use with boards without a Zynq chip. For Zynq boards, the Zynq7 Processing System should be used instead.

**Note:** If you aren't sure whether your board has DDR memory, check the Memory column of the specification table on this site's <u>Programmable Logic</u> (https://digilent.com/reference/programmable-logic/start) page.

#### Follow the steps in this dropdown for boards without DDR memory

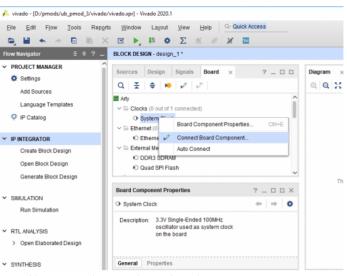

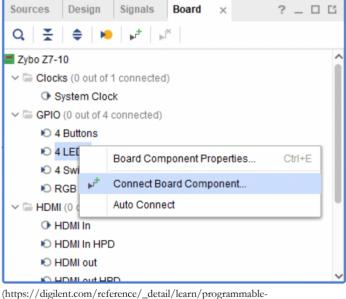

First, an external clock should be added to the block design, so that it can be used to generate any other clocks required by the design. Open the **Board** tab, and find the system clock. Right-click on it and select **Connect Board Component**.

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/add-microblaze-processor/microblaze-1.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

In the *Connect Board Component* dialog, select the CLK\_IN1 of a new Clocking Wizard IP. This will add a clocking wizard to the design, which can be used to easily configure the board's MMCMs and PLLs to generate any required clocks. Click **OK** to continue.

| 🝌 Connect Board Compo      | nent                          |              | ×      |

|----------------------------|-------------------------------|--------------|--------|

| Select one or more pins to | o connect board component "Sy | stem Clock'. | A      |

| Q ≚ ≑                      |                               |              |        |

| Name                       | VLNV                          |              |        |

| Create new IP              |                               |              |        |

|                            | ard xilinx.com:ip:clk_wiz:6.0 |              |        |

| $\checkmark$ $\gg$ clock_  | CLK_IN1                       |              |        |

| □ » clock_                 | CLK_IN2                       |              |        |

|                            |                               |              |        |

|                            |                               | ОК           | Cancel |

| https://digilent.com/ref   | erence/_detail/learn/progr    | ammable-     |        |

logic/tutorials/2020.1/add-microblaze-processor/microblaze-2.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

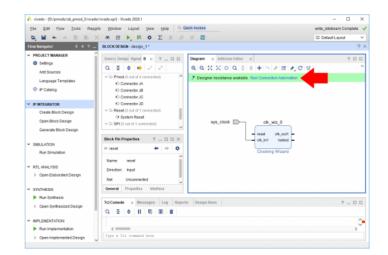

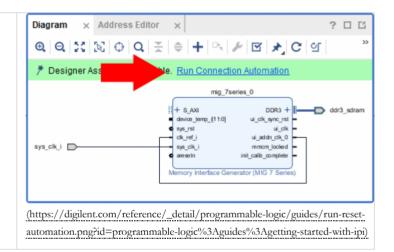

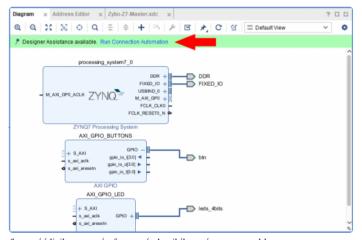

Next, an external reset port should be added to the design that can be used to reset the entire system. Click the **Run Connection Automation** button in the green *Designer Assistance* toolbar.

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/add-microblaze-processor/microblaze-3.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

| In the Run Connection Automation dialog, in the list on the left side of the |

|------------------------------------------------------------------------------|

| dialog, make sure that the Clocking Wizard's reset box is checked. The       |

| Select Board Part Interface dropdown lists any options for resets that are   |

| specified in your board's board files. For most boards, only one option      |

| will be available. Click <b>OK</b> to continue.                              |

| a  <u>∓</u>   ≑                                            | Description                                                                  |  |

|------------------------------------------------------------|------------------------------------------------------------------------------|--|

| ✓ All Automation (1 out of<br>✓ ♥ ♥ clk_wiz_0<br>♥ ≫ reset | Connect Board Part Interface to IP Interface.<br>Interface: /clk_wiz_0/reset |  |

|                                                            | Options                                                                      |  |

|                                                            | Select Board Part Interface reset (System Reset) v                           |  |

|                                                            |                                                                              |  |

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/add-microblaze-processor/microblaze-4.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

Note: Depending on the polarity of the reset button (active high or active low), a Utility Vector Logic IP may be inserted between the reset port and the Clocking Wizard. This is used to ensure that the active high reset pin of the IP is provided with the correct polarity of reset signal, and that the design will not be held in reset while the reset button is not pressed.

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/add-microblaze-processor/microblaze-5.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

Your design will require at least one clock from the clocking wizard. If your design requires more clocks, then they must be added through the Clocking Wizard.

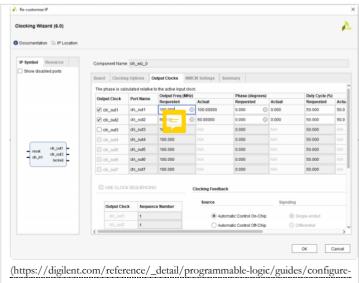

Double click on the Clocking Wizard IP core to edit its settings. Navigate to the *Output Clocks* tab. Additional clocks are added to the Clocking Wizard by checking a box in the *Output Clock* column, and specifying a *Requested Output Frequency*. Additionally, if desired, the ports can be named according to their intended purpose.

If your design requires additional clocks (such as for an ext\_spi\_clock pin), they should be added now.

Click OK to confirm your changes to the Clocking Wizard's settings.

If you aren't sure that you have all of the clocks you need, don't worry, you can always come back and add them by reconfiguring this IP. This task can be performed whenever in the design process it becomes necessary.

| P Symbol Resource     | Component Nan   | ne dk_wiz_0        |                          |          |               |                       |   |        |

|-----------------------|-----------------|--------------------|--------------------------|----------|---------------|-----------------------|---|--------|

| 3 Show disabled ports | Board Clock     | ing Options        | Output Clocks            | MMC      | M Settings    | Summary               |   |        |

|                       | The phase is ca | alculated relative | to the active inp        | ut clock |               |                       |   |        |

|                       | Output Clock    | Port Name          | Output Freq<br>Requested | (MHz)    | Actual        | Phase (de<br>Requeste |   | Actual |

|                       | Cik_out1        | clk_out1           | 100.000                  | 0        |               | 0.000                 | 0 |        |

|                       | Clk_out2        | clk_out2           | 100.000                  |          |               | 0.000                 |   |        |

|                       | Clk_out3        | clk_out3           | 100.000                  |          | NIA           | 0.000                 |   | N/A    |

| reset clk_out1        | clk_out4        | clk_out4           | 100.000                  |          | NIA           | 0.000                 |   |        |

| clk_in1 locked        | clk_out5        | clk_out5           | 100.000                  |          | NIA           | 0.000                 |   | N/A    |

|                       | clk_out6        | clk_out6           | 100.000                  |          | NIA           | 0.000                 |   |        |

|                       | Clk_out7        | clk_out7           | 100.000                  |          |               | 0.000                 |   |        |

|                       |                 |                    |                          |          |               |                       |   |        |

|                       | USE CLO         | CK SEQUENCI        | IG                       | c        | locking Feedb | ack                   |   |        |

(https://digilent.com/reference/\_detail/reference/programmable-

logic/guides/microblaze-8.png?id=programmable-logic%3Aguides%3Agettingstarted-with-ipi)

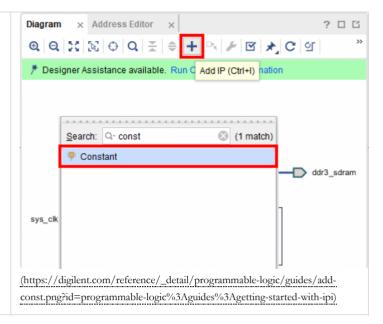

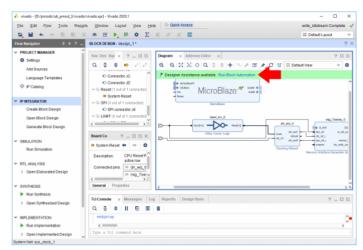

Next, use the **Add IP** button (+) to add the *MicroBlaze* IP to the design. The block that is added represents the core of the Microblaze processor.

(https://digilent.com/reference/\_detail/learn/programmable-

logic/tutorials/2020.1/add-microblaze-processor/microblaze-12.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

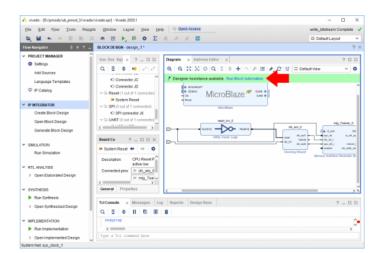

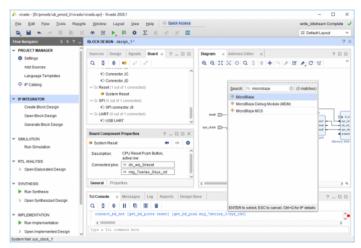

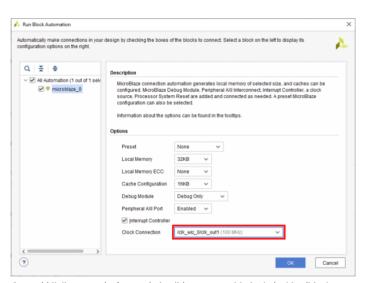

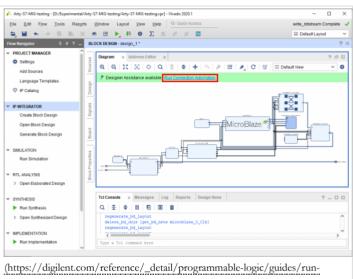

Next, block automation will be run so that additional supporting infrastructure can be added to the design. Click **Run Block Automation** in the green *Designer Assistance* bar.

**Note:** The screenshot to the right is not representative for a design not using DDR, as these designs will not contain a MIG IP core.

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/add-microblaze-processor/microblaze-13.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi) In the *Run Block Automation* dialog, several settings can be specified for how the Microblaze IP will be connected to the rest of the design:

- Local Memory specifies how much block <u>RAM.()</u> memory will be dedicated to the processor. DDR-less designs require more memory, and the amount of memory necessary depends heavily on the size of the software application being run. 32KB is enough for many small applications.

- Cache Configuration can help the speed of designs using DDR memory. It should be enabled when using DDR and disabled otherwise.

- **Debug Module** allows you to specify the capabilities of the debugger. The default *Debug Only* option is recommended.

- **Peripheral AXI Port** enables or disables the AXI master interface of the processor. It must be enabled to allow the processor to be connected to hardware peripherals.

- Interrupt Controller specifies whether the processor can be interrupted by its peripherals. Whether or not it needs to be enabled depends on your design requirements. If any IP that you intend to connect to the processor must have interrupts to function correctly, the box must be checked.

- Clock Connection specifies the processor's clock. Designs using DDR should use the MIG's ui\_clk pin, while designs without DDR should use the Clocking Wizards clk\_out1 pin.

# **Note:** Settings not present in this list are out of the scope of this guide, and can safely be left as their default.

Confirm that the settings meet your design requirements. It should be noted that while it is possible to change these settings manually later (for example, by manually adding an AXI INTC IP and connecting it to the processor), the easiest way to do so will be to clear the Microblaze processor out of your block design and restart the process of adding the processor. This is to say, the settings chosen here are important. Getting them right the first time will save you time in the long run.

Click OK to continue.

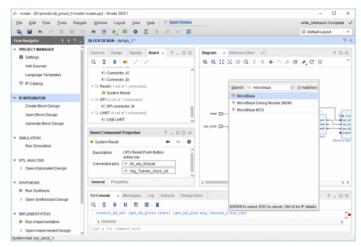

Next, in order for the software design to be able to print to a serial console on a host computer, a UART peripheral must be connected. Find the *USB UART* interface in the *Board* tab, right click on it, and select **Connect Board Component**.

|                                                         | n by checking the boxes of the b                                                                                        | oons to contract o                        | elect a bio                |                               | to aropidy no   | comparator     | space of the right | 1  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------|-------------------------------|-----------------|----------------|--------------------|----|

| Q <u>≭</u> ¢                                            | Description                                                                                                             |                                           |                            |                               |                 |                |                    |    |

| ✓ All Automation (1 out of 1 selected) ✓ ♥ microblaze_0 | MicroBlaze connection au<br>MicroBlaze Debug Moduli<br>are added and connected<br>Information about the opti<br>Options | e, Peripheral AXI In<br>as needed. A pres | terconnect,<br>set MicroBl | Interrupt Co<br>aze configura | ntroller, a clo | ck source, Pro |                    | et |

|                                                         | Preset                                                                                                                  | None                                      | ~                          |                               |                 |                |                    |    |

|                                                         | Local Memory                                                                                                            | 32KB v                                    |                            |                               |                 |                |                    |    |

|                                                         | Local Memory ECC                                                                                                        | None v                                    |                            |                               |                 |                |                    |    |

|                                                         | Cache Configuration                                                                                                     | 16KB ~                                    |                            |                               |                 |                |                    |    |

|                                                         | Debug Module                                                                                                            | Debug Only                                | ~                          |                               |                 |                |                    |    |

|                                                         | Peripheral AXI Port                                                                                                     | Enabled v                                 |                            |                               |                 |                |                    |    |

|                                                         | Interrupt Controller                                                                                                    |                                           |                            |                               |                 |                |                    |    |

|                                                         | Clock Connection                                                                                                        | /mig_7series_0                            | <b>ui_dk</b> (83           | MHz) 🗸                        |                 |                |                    |    |

|                                                         |                                                                                                                         |                                           |                            |                               |                 |                |                    |    |

|                                                         |                                                                                                                         |                                           |                            |                               |                 |                |                    |    |

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/add-microblaze-processor/microblaze-14.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/add-microblaze-processor/microblaze-18.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi) In the dialog that pops up, select a new AXI Uartlite IP's UART interface, and click **OK** to add the block to the diagram.

| elect an IP block interface for connecting board | d component 'USB UART'.          |

|--------------------------------------------------|----------------------------------|

| Q   ₹   ≑                                        |                                  |

| Name                                             | VLNV                             |

| + AXI Uartlite                                   | xilinx.com:ip:axi_uartlite:2.0   |

| UART                                             |                                  |

| AXI UART16550                                    | xilinx.com:ip:axi_uart16550:2.0  |

| UART                                             |                                  |

| + IOModule                                       | xilinx.com:ip:iomodule:3.1       |

| UART                                             |                                  |

| HicroBlaze MCS                                   | xilinx.com:ip:microblaze_mcs:3.0 |

| UART                                             |                                  |

| ThD Coff Error Mitigation Interface              | viliny compiniting comit 0       |

|                                                  | OK Cancel                        |

logic/tutorials/2020.1/add-microblaze-processor/microblaze-19.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

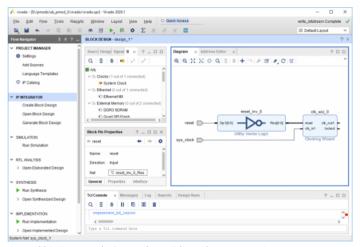

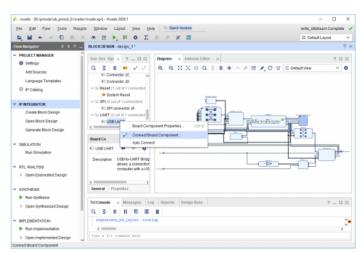

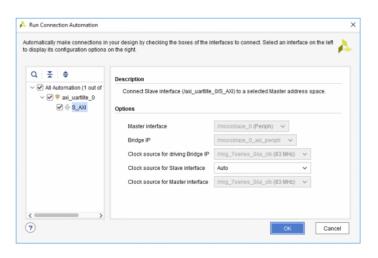

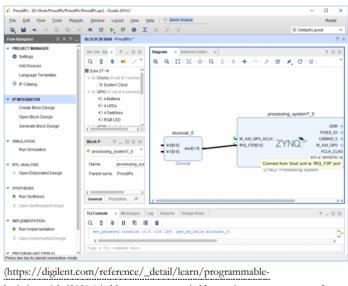

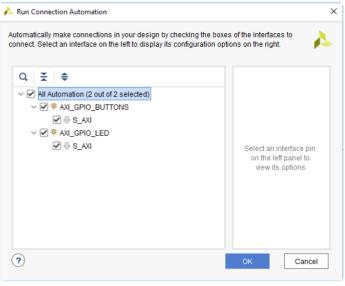

To connect all remaining AXI cores that have not yet been connected to the processor, click the **Run Connection Automation** button in the green *Designer Assistance* bar. Check the *All Automation* box in the list on the left side of the window to select all of the remaining AXI cores. The dropdown settings available for each core can safely be left as their default values. Click **OK** to automatically connect them to the processor.

| Q ≚ ≑                                               | Description                            |                                    |             |

|-----------------------------------------------------|----------------------------------------|------------------------------------|-------------|

| ✓ ✓ All Automation (1 out of<br>✓ ✓ ≠ axi_uartite_0 | Connect Slave interface (/axi_uartlite | _0/S_AXI) to a selected Master add | ress space. |

| S_AXI                                               | Options                                |                                    |             |

|                                                     | Master interface                       | /microblaze_0 (Periph) v           |             |

|                                                     | Bridge IP                              | /microblaze_0_axi_periph 🗸         |             |

|                                                     | Clock source for driving Bridge IP     | /mig_7series_0/ui_clk (83 MHz)     | ~           |

|                                                     | Clock source for Slave interface       | Auto                               | ~           |

|                                                     | Clock source for Master interface      | /mig_7series_0/ui_clk (83 MHz)     | ~           |

|                                                     |                                        |                                    |             |

|                                                     |                                        |                                    |             |

| )                                                   |                                        | ок                                 | Cancel      |

|                                                     |                                        |                                    |             |

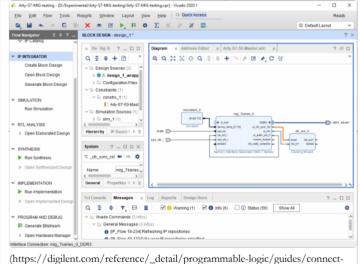

## Follow the steps in this dropdown for boards with DDR memory

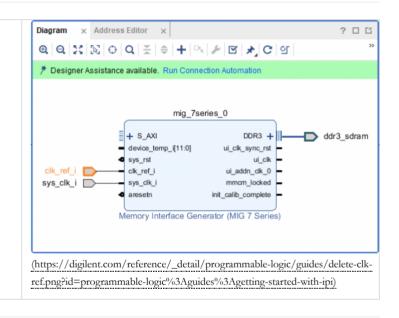

When creating a design with DDR, it's best to add the DDR interface first, as it is typically also used to generate the clock or clocks that will be used by the rest of your design.

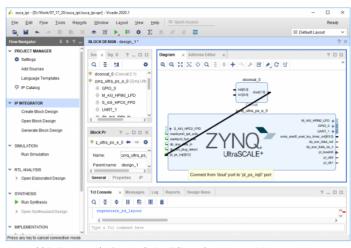

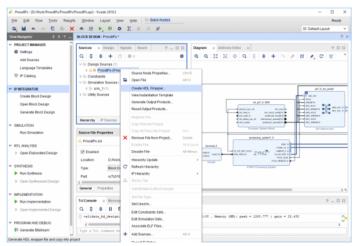

In the Board tab, right click on the DDR interface and select "Auto Connect". This process will add a MIG and the external DDR interface to the design. Two clock pins are also created, which will need to be modified.

| E, 🖬 🔸 🤌 🖬 🐘 🔅                                                      | ✓ ☑ ▶, 48 Φ ∑ ≤ Ø Ø ☑ BLOCK DESIGN - design 1*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I Default Layout                                                                                                                                                               |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                     | BLOCK DESIGN - design_1 *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                |

| PROJECT MANAGER     Settings     Add Sources     Language Templates | Sources         Design         Signals         Board         ×         ?          C           Q         ∑         ÷         is         is | Diagram         ×         Address Editor         ×         ?         □           Q         Q         X         X         Q         Z         +         N         F         III |

| P IP Catalog                                                        | O DDR Clock<br>O System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                |

| P INTEGRATOR                                                        | External Memory (0 out of 2 connected)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                |

| Create Block Design<br>Open Block Design                            | DDR3 SC <sup>maxx</sup> Board Component Properties Ctri+E     GPID (0 out a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                |

| Generate Block Design                                               | © 2 RGB LE Auto Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | This design is empty. Press the 🕂 button to add IP.                                                                                                                            |

| <ul> <li>SIMULATION</li> <li>Run Simulation</li> </ul>              | © 4 LEDs<br>© 4 Push Butions<br>© 4 Switches<br>© Shield Pins 0 through 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                |

| RTL ANALYSIS     Open Elaborated Design                             | Board Component Properties         ? _ □ □ ×           • ○ DDR3 SDRAM         ← ⇒ ◊                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                |

| SYNTHESIS                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                |

| Run Synthesis                                                       | Tcl Console × Messages Log Reports Design Runs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ? _ □                                                                                                                                                                          |

| > Open Synthesized Design                                           | Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                |

| MPLEMENTATION                                                       | <pre>set_property -dict [list CONFIG.CONST_WIDIH [12] CONFIG.<br/>connect bd net [get bd pins xlconstant 0/dout] [get bd pins<br/></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                |

| Run Implementation                                                  | Type a Tcl command here                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                |

| uto Connect                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                |

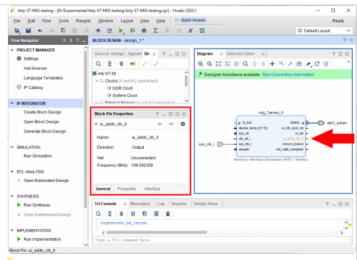

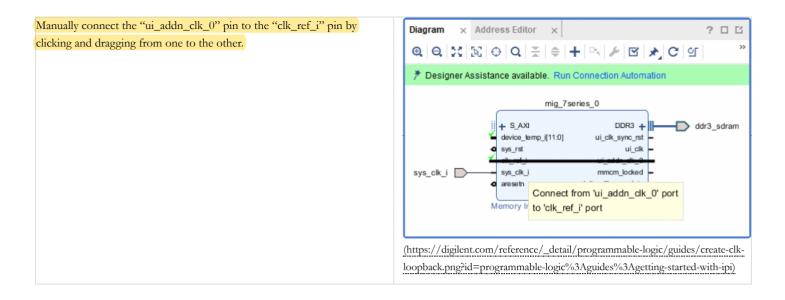

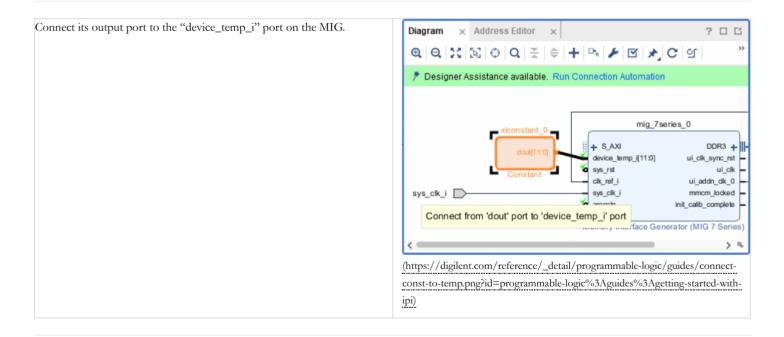

Delete the "clk\_ref\_i" pin. This can be accomplished either by rightclicking on the pin and selecting delete or by selecting and pressing the delete key.

Verify that the "ui\_addn\_clk\_0" pin has a frequency near 200 <u>MHz\_0</u> by selecting it and looking at the "Frequency" value in the "Block Pin Properties" pane.

(https://digilent.com/reference/\_detail/programmable-logic/guides/check-uiaddn-clk-properties.png?id=programmable-logic%3Aguides%3Agetting-startedwith-ipi)

It's important to note that the "sys\_clk\_i" pin will not be constrained by the board files, and you will need to add a constraint file to map it to the corresponding pin location on the FPGA.

If your project doesn't contain the master Xilinx Design Constraint (XDC) file for your board, the dropdown below details how to add it. This file contains the constraints that your board places on designs using it - specific interfaces wired up to specific pins, clock frequencies, and FPGA bank voltages, for some examples. Click the dropdown below for a walkthrough of how to add this file to your project.

#### Add a Master XDC File to a Vivado Project

Download and extract digilent-xdc-master.zip (https://digilent.com/reference/lib/exe/fetch.php? tok=a49a20&media=https%3A%2F%2Fgithub.com%2FDigilent%2Fdigilentxdc%2Farchive%2Fmaster.zip). This file includes all of the latest template XDC files released for Digilent's boards, which are available on Github in the 🚱 digilent-xdc (https://github.com/Digilent/digilent-xdc) repository.

| 🔄 🔜 ∓   digilent-xdi<br>Ie Home Share | c-master<br>View |                                           |                    |          | -    | · •       |

|---------------------------------------|------------------|-------------------------------------------|--------------------|----------|------|-----------|

| → ~ 个 📙 → This                        | PC > Download    | ls > digilent-xdc-master > digilent-xdc-r | master             |          | v õ  | Search di |

| Ouick access                          | ^                | Name                                      | Date modified      | Туре     | Size |           |

|                                       |                  | Arty-A7-35-Master.xdc                     | 6/18/2020 10:43 AM | XDC File |      | 22 KB     |

| Desktop                               |                  | Arty-A7-100-Master.xdc                    | 6/18/2020 10:43 AM | XDC File |      | 21 KB     |

| 👆 Downloads                           | *                | Arty-Master.xdc                           | 6/18/2020 10:43 AM | XDC File |      | 21 KB     |

| Documents                             |                  | Arty-S7-25-Rev-E-Master.xdc               | 6/18/2020 10:43 AM | XDC File |      | 18 KB     |

| E Pictures                            |                  | Arty-S7-50-Rev-B-Master.xdc               | 6/18/2020 10:43 AM | XDC File |      | 18 KB     |

| Github                                | *                | Arty-S7-50-Rev-E-Master.xdc               | 6/18/2020 10:43 AM | XDC File |      | 18 KB     |

| Data (D:)                             |                  | Arty-Z7-10-Master.xdc                     | 6/18/2020 10:43 AM | XDC File |      | 15 KB     |

| Dotte (D.)                            | ~                | Arty-Z7-20-Master.xdc                     | 6/18/2020 10:43 AM | XDC File |      | 18 KB     |

| OneDrive                              |                  | Basys-3-Master.xdc                        | 6/18/2020 10:43 AM | XDC File |      | 13 KB     |

| This PC                               |                  | Cmod-A7-Master.xdc                        | 6/18/2020 10:43 AM | XDC File |      | 13 KB     |

| 3D Objects                            |                  | Cmod-S7-25-Master.xdc                     | 6/18/2020 10:43 AM | XDC File |      | 8 KB      |

|                                       |                  | Cora-Z7-07S-Master.xdc                    | 6/18/2020 10:43 AM | XDC File |      | 14 KB     |

| Desktop                               |                  | Cora-Z7-10-Master.xdc                     | 6/18/2020 10:43 AM | XDC File |      | 14 KB     |

| Documents                             |                  | Z Eclypse-Z7-Master.xdc                   | 6/18/2020 10:43 AM | XDC File |      | 11 KB     |

| 👆 Downloads                           |                  | Genesys-2-Master.xdc                      | 6/18/2020 10:43 AM | XDC File |      | 46 KB     |

| 👌 Music                               |                  | Genesys-ZU-3EG-Master.xdc                 | 6/18/2020 10:43 AM | XDC File |      | 25 KB     |

| E Pictures                            |                  | Z License.txt                             | 6/18/2020 10:43 AM | TXT File |      | 2 KB      |

| Videos                                |                  | Nexys-4-DDR-Master.xdc                    | 6/18/2020 10:43 AM | XDC File |      | 20 KB     |

| Local Disk (C:)                       |                  | Nexys-4-Master.xdc                        | 6/18/2020 10:43 AM | XDC File |      | 38 KB     |

| Data (D:)                             |                  | Wexys-A7-50T-Master.xdc                   | 6/18/2020 10:43 AM | XDC File |      | 20 KB     |

| a Data (D:)                           |                  | Nexys-A7-100T-Master.xdc                  | 6/18/2020 10:43 AM | XDC File |      | 20 KB     |

|                                       |                  | Nexys-Video-Master.xdc                    | 6/18/2020 10:43 AM | XDC File |      | 29 KB     |

|                                       | ~                | Sword-Master.xdc                          | 6/18/2020 10:44 AM | XDC File |      | 53 KB     |

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/add-gpio-to-block-design/extracted-xdc-folder.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

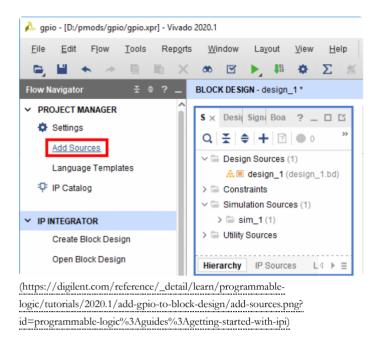

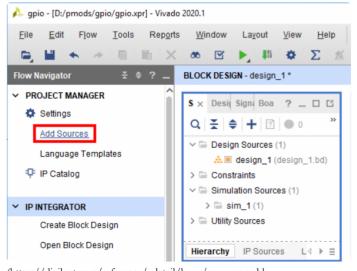

Returning to Vivado, click the **Add Sources** button in the *Project Manager* section of the *Flow Navigator* pane. This will launch a dialog that you can use to add a variety of types of source files to the project (or create new ones).

On the first screen, select Add or create constraints. Click Next to continue.

id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

In the next screen, make sure that the constraint set specified (the one that the master XDC will be added to) is set to *constrs\_1*, and that it is the *active* set. Click the **Add Files** button.

| Specify constraint set | e constrs_1 (active) | ~                    |                        |  |  |

|------------------------|----------------------|----------------------|------------------------|--|--|

|                        |                      | Use Add Files or Cre | ate File buttons below |  |  |

|                        |                      | Add Files            | Create File            |  |  |

(https://digilent.com/reference/\_detail/learn/programmablelogic/tutorials/2020.1/add-gpio-to-block-design/add-files.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi) In the dialog that pops up, navigate to the folder that the *digilent-xdc-master.zip* file was extracted into. Highlight the XDC file for your board, then click **OK** to continue.

| ook in: 🔚 digilent-xdc-master                     |                                                                                                                  |  |  |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|

| Arty-A7-35-Master.xdc Nexys-A7-100T-Master.xdc    | Recent Directories                                                                                               |  |  |

| Arty-Master.xdc Sword-Master.xdc                  | DJpmods/zyng_pmod                                                                                                |  |  |

| Arty-S7-25-Rev-E-Master.xdc                       | File Preview                                                                                                     |  |  |

| Arty-S7-50-Rev-B-Master.xdc 📗 Zedboard-Master.xdc |                                                                                                                  |  |  |

| 🗋 Arty-S7-50-Rev-E-Master.xdc 📘 Zybo-Master.xdc   | ## It is compatible with the Sybo 27-20 and Sybo 27-10                                                           |  |  |

| Arty-Z7-10-Master.xdc                             | ## To use it in a project:<br>## - uncomment the lines corresponding to used pins                                |  |  |

| Arty-Z7-20-Master.xdc                             | ## - uncomment the lines corresponding to used pins<br>## - rename the used ports (in each line, after get por   |  |  |

| Basys-3-Master.xdc                                |                                                                                                                  |  |  |

| Cmod-A7-Master.xdc                                | ##Clock signal                                                                                                   |  |  |

| Cmod-S7-25-Master.xdc                             | #set_property -dict ( PACKAGE FIN K17 IOSTANDARD LVCM<br>#create clock -add -name sys clk pin -period 8.00 -vave |  |  |

| Cora-Z7-07S-Master.xdc                            | for the state of the period of the state                                                                         |  |  |

| Cora-Z7-10-Master.xdc                             |                                                                                                                  |  |  |

| Eclypse-Z7-Master.xdc                             | ##Switches<br>#set property -dict ( PACKAGE PIN G18 IOSTANDARD LVCM                                              |  |  |

| Genesys-2-Master.xdc                              | #set property -dict ( PACKAGE PIN 918 IOSTANDARD LVCM                                                            |  |  |

| Genesys-ZU-3EG-Master.xdc                         | #set property -dict { PACKAGE PIN W13 IOSTANDARD LVCM                                                            |  |  |

| Nexys-4-DDR-Master.xdc                            | #set_property -dict { PACKAGE_PIN T16 IOSTANDARD LVCM                                                            |  |  |

| Nexys-4-Master.xdc                                |                                                                                                                  |  |  |

| Nexys-A7-50T-Master.xdc                           | 44Ruttons                                                                                                        |  |  |

| le name: Zybo-Z7-Master.xdc                       |                                                                                                                  |  |  |

| les of type: Design Constraint Files (.sdc, xdc)  |                                                                                                                  |  |  |

|                                                   |                                                                                                                  |  |  |

|                                                   | OK Cance                                                                                                         |  |  |

logic/tutorials/2020.1/add-gpio-to-block-design/find-xdc.png? id=programmable-logic%3Aguides%3Agetting-started-with-ipi)

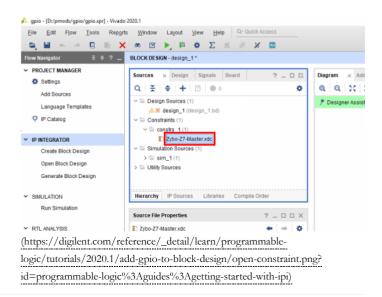

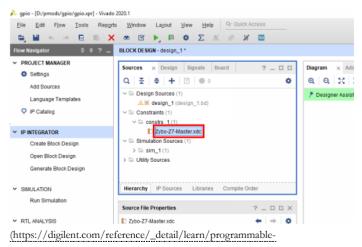

Back in the *Add Sources* dialog, make sure that your chosen constraint file appears in the table. Also, make sure that the *Copy constraint files into project* box is checked. If this box is unchecked, the file will be linked by your project, and any modifications made within the project will affect the version you downloaded. Since you may need to use this file again in other projects, copying the constraint file is recommended, so that you can always work from a fresh copy.

Click Finish to add the constraint file to your project.

| d or Create Cons        | rainte                                           |                           |            |            |

|-------------------------|--------------------------------------------------|---------------------------|------------|------------|

|                         | nt files for physical and timing constraint to a | add to your project.      |            |            |

|                         |                                                  |                           |            |            |

|                         |                                                  |                           |            |            |

| Specify constraint set: | 🗁 constrs_1 (active) 🗸 🗸                         |                           |            |            |

| $+_{1} =  +  = 1$       | ,                                                |                           |            |            |

| Constraint File         | Location                                         |                           |            |            |

| Zybo-Z7-Master.xdc      | C:\Users\arthur\Downloads\digilent-xdc-m         | aster\digilent-xdc-master |            |            |

|                         |                                                  |                           |            |            |

|                         |                                                  |                           |            |            |

|                         |                                                  |                           |            |            |

|                         |                                                  |                           |            |            |

|                         |                                                  |                           |            |            |

|                         |                                                  |                           |            |            |

|                         |                                                  |                           |            |            |

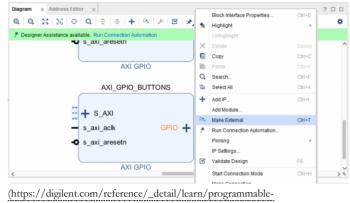

|                         |                                                  |                           |            |            |