# Transactional Memory: An Overview (part II)

Written by Harris et al.

### Another Example

#### a = 20, b = 50, c = 0

down(mutex); a = a + 20; b = b - 10;c = c - b;up(mutex);

**T**7 down(mutex); b = b + 20;c = c + b; up(mutex);

### Another Example

#### a = 20, b = 50, c = 0

... down(mutex); a = a + 20; b = b - 10; c = c - b; up(mutex); T2 ... down(mutex); b = b + 20; c = c + b; up(mutex);

if T1 before T2 a = 40 b = 60 c = 20 if T2 before T1 a = 40

### Another Example

#### a = 20, b = 50, c = 0

... begin TX a = a + 20; b = b - 10; c = c - b; end TX T2 ... begin TX b = b + 20; c = c + b; end TX if T1 commits before T2 a = 40 b = 70 c = 70

if T2 commits before T1 a = 40 b = 40 c = -50

#### a = 20, b = 50, c = 0

... begin TX a = a + 20; b = b - 10; c = c - b; end TX

**T2** begin TX b = b + 20; c = c + b;end TX

•••

#### a = 20, b = 50, c = 0

T1

RS

$$a = 2$$

...

begin TX

$a = a + 20$ ;

$b = b - 10$ ; ws

$a = 4$

end TX

T2

$$rac{1}{1}$$

RS

$begin TX$

$b = b + 20$ ;

$c = c + b$ ;

end TX

...

...

#### a = 20, b = 50, c = 0

T1

RS

$$a = 2$$

$b = 5$

$b = b$

$b = b - 10$ ; WS

$a = 4$

$b = 4$

$b = 4$

RS **T2** begin TX b = b + 20; c = c + b; end TX

#### a = 20, b = 50, c = 0

T1

RS

$$a = 20$$

$a = 20$

$begin TX$

$b = 50$

$b = a + 20$ ;

$b = 40$

$a = a + 20$ ;

$c = 0$

$b = b - 10$ ;

WS

$c = c - b$ ;

$a = 40$

$b = 40$

$c = -40$

T2

$$T2$$

$begin TX$

$b = b + 20$ ;

$c = c + b$ ;

$end TX$

...

•••

#### a = 20, b = 50, c = 0

#### a = 20, b = 50, c = 0

T1

RS

$$a = 20$$

$a = 20$

$begin TX$

$b = 50$

$b = a + 20$ ;

$b = 40$

$a = a + 20$ ;

$b = 40$

$b = b - 10$ ;

WS

$c = c - b$ ;

$a = 40$

$b = 40$

$c = -40$

RS b = 40 **T2** begin TX **b** = **b** + 20; **c** = **c** + **b**; **w**S **b** = 60 end TX

$\bullet \bullet \bullet$

#### a = 20, b = 50, c = 0

T1

RS

$$a = 20$$

$a = 20$

$begin TX$

$b = 50$

$a = a + 20$ ;

$b = 40$

$b = b - 10$ ;

$ws$

$c = c - b$ ;

$a = 40$

$b = 40$

$c = 0$

$c = -40$

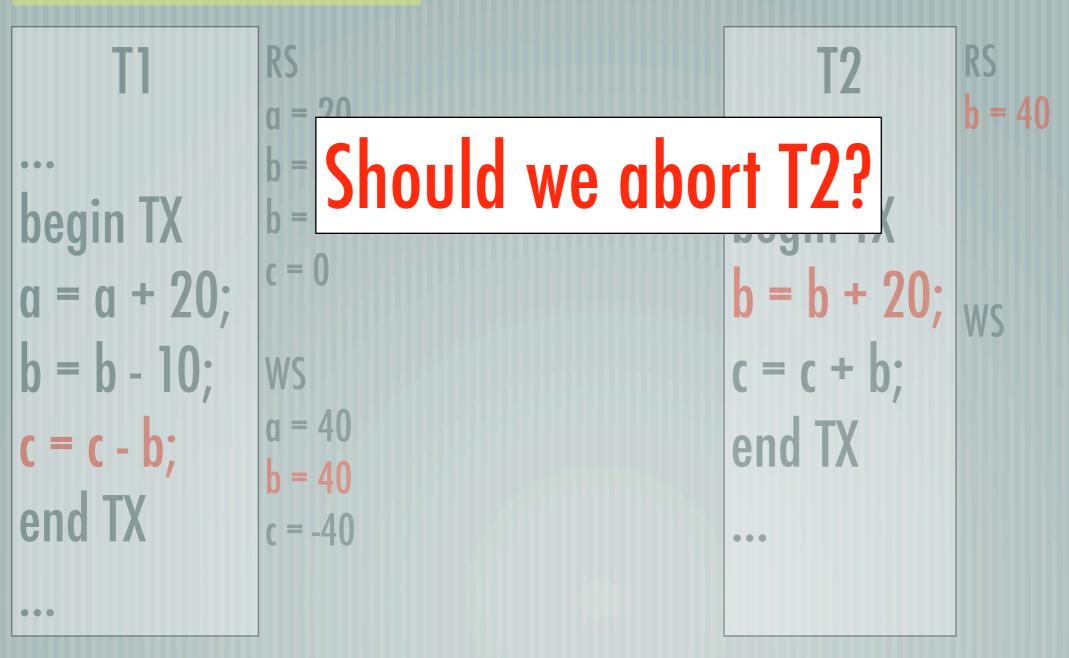

# T1 commits first so the result in T2 is fine. What happen to both transactions if T2 commits first?

a = 20, b = 50, c = 0

T1

RS

$$a = 20$$

$begin TX$

$a = a + 20$ ;

$b = b - 10$ ;

$ws$

$c = c - b$ ;

$end TX$

slightly behind T1 RS b = 50 **T2** begin TX b = b + 20; c = c + b; end TX

#### a = 20, b = 50, c = 0

T1

RS

$$a = 20$$

$begin TX$

$a = a + 20$ ;

$b = b - 10$ ;

$ws$

$c = c - b$ ;

$end TX$

RS b = 50 **T2** begin TX b = b + 20; c = c + b; end TX

#### a = 20, b = 50, c = 0

T1

RS

$$a = 20$$

$a = 20$

begin TX

$b = 50$

begin TX

$b = 50$

$a = a + 20$ ;

$WS$

$b = b - 10$ ;

$WS$

$c = c - b$ ;

$a = 40$

end TX

$b = 40$

$$\begin{array}{c}

T2 \\

Abort T2 \\

... \\

begin TX \\

b = b + 20; \\

c = c + b; \\

end TX \\

... \\

\end{array}$$

WS

...

# Another Example (lazy)

#### a = 20, b = 50, c = 0

T1

RS

$$a = 20$$

$a = 20$

$begin TX$

$b = 50$

$begin TX$

$b = 40$

$a = a + 20$ ;

$b = 40$

$b = b - 10$ ;

WS

$c = c - b$ ;

$a = 40$

$b = 40$

$c = -40$

RS b = 50 **T2** begin TX b = b + 20; c = c + b; b = 70 end TX

# Another Example (lazy)

#### a = 20, b = 50, c = 0

T]

RS

$$a = 20$$

$b = 50$

$b = 50$

$b = 50$

$b = 40$

$c = 0$

$c = 0$

WS

$a = 40$

$b = 40$

$c = 0$

WS

$a = 40$

$b = 40$

$c = -0$

WS

$a = 40$

$b = 40$

$c = -0$

T2

$$T2$$

$begin TX$

$b = b + 20;$

$c = c + b;$

end TX

...

# Another Example (lazy)

#### a = 20, b = 50, c = 0

T1RS

$$a = 20$$

$begin TX$  $a = a + 20$ ; $b = b - 10$ ; $b = b - 10$ ; $c = c - b$ ; $a = 40$  $b = 40$  $c = -40$

RS **T2** b = 50 b = 70 begin TX c = 0 b = b + 20; <sub>WS</sub> c = c + b; b = 70c = -70 end TX Abort T2

#### Minimalist

modifying cache consistency protocol

extending instruction set architecture

keep speculative state in a buffer

#### [ ISA support

- delimiter instructions (STR and ETR)

- special load and store (TLD and TST)

- abort and validation (ABR and VLD)

- VLD is used for eager versioning

- Buffer or cache modifications

- store speculative states in hardware buffer or extended cache

- word level or cache-line level

- **Herlihy and Moss**

- read set and write set in data cache

- transactional cache

- two additional bits per cache line

- discard pre-transaction values or discard speculative values

- **Two approaches**

- separation of ordinary data and transactional data

- all data are ordinary but separate metadata structure for transactional data

#### Transactional data

- store in object headers

- special methods (openforread, openforwrite) to dynamically build read set and write set

- private shadow copy of each object for each transaction

#### Metadata for transactional objects

special methods (openforreading, openforwriting) to track transactional accesses to ordinary objects

- **Detecting conflicts**

- two-phase locking

- acquire lock at the beginning of transaction and relinquish lock at the end

- hybrid

- lock on write, version control on read

### Summary

Relieve the programmer's burden of coordinating parallelism offload the responsibility to runtime systems conflict detection and resolution **Can be implemented in hardware and software** More details to follow in subsequent meetings