CSCE 230J Computer Organization

# Processor Architecture IV: Pipelined Implementation

Dr. Steve Goddard goddard@cse.unl.edu

http://cse.unl.edu/~goddard/Courses/CSCE230J

# Giving credit where credit is due

- Most of slides for this lecture are based on slides created by Dr. Bryant, Carnegie Mellon University.

- ■I have modified them and added new slides.

2

# Real-World Pipelines: Car Washes Sequential Parallel Pipelined Idea Divide process into independent stages Move objects through stages in sequence At any given time, multiple objects being processed

# **Pipeline Summary**

### Concept

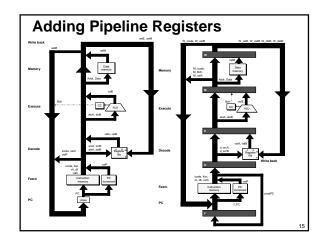

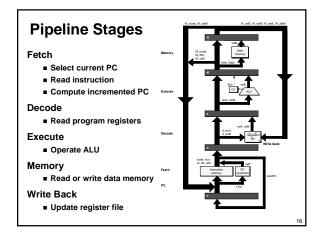

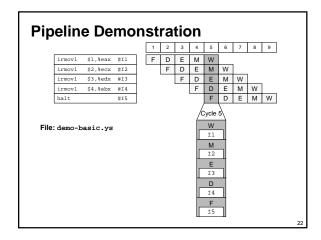

- Break instruction execution into 5 stages

- Run instructions through in pipelined mode

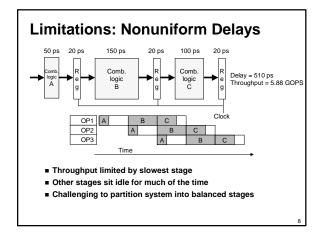

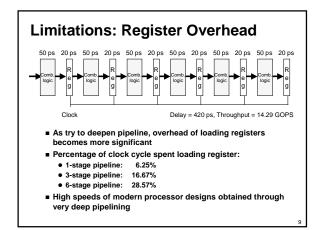

## Limitations

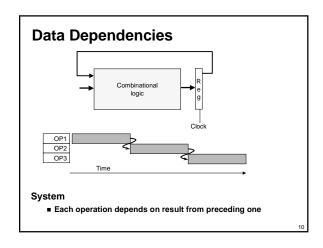

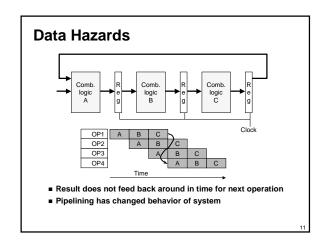

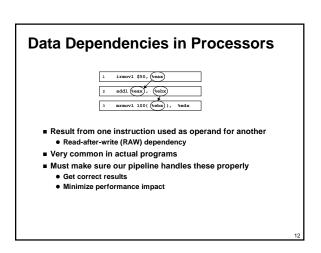

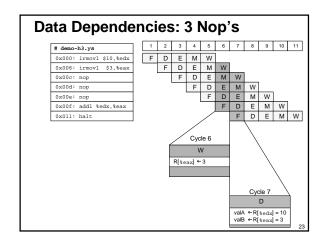

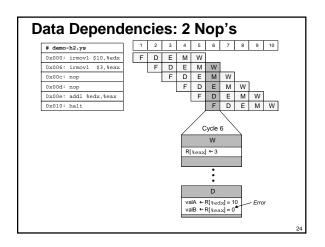

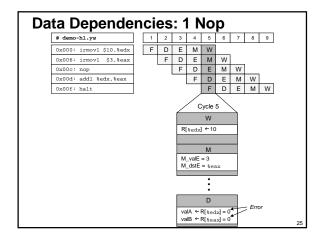

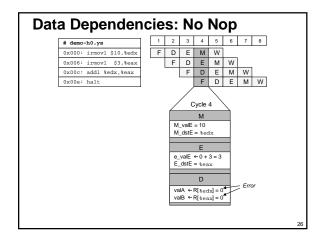

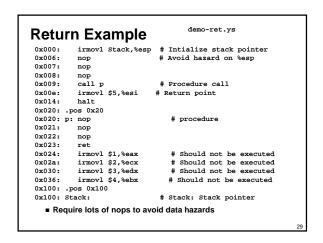

- Can't handle dependencies between instructions when instructions follow too closely

- Data dependencies

- One instruction writes register, later one reads it

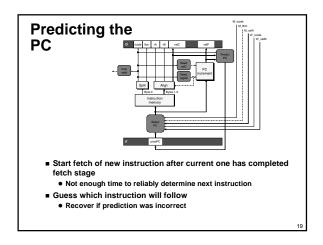

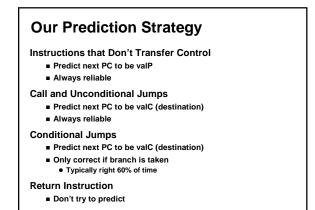

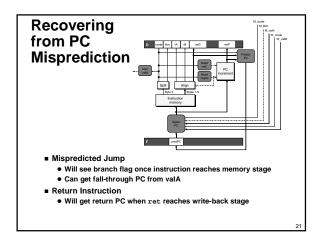

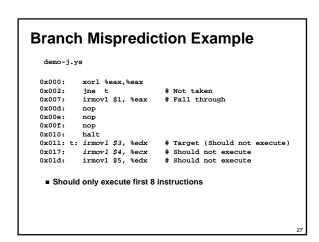

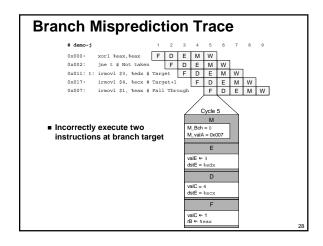

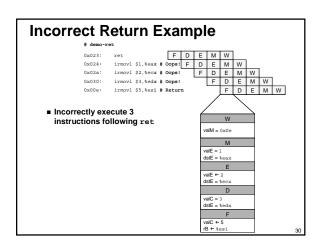

- Control dependency

Instruction sets PC in way that pipeline did not predict correctly

Mispredicted branch and return

### Fixing the Pipeline

■ We'll do that next