CSCE 230J Computer Organization

### Processor Architecture I: Y86 Instruction Set Architecture

Dr. Steve Goddard goddard@cse.unl.edu

http://cse.unl.edu/~goddard/Courses/CSCE230J

# Giving credit where credit is due

- Most of slides for this lecture are based on slides created by Dr. Bryant, Carnegie Mellon University.

- I have modified them and added new slides.

# **Chapter Outline**

#### Background

- Instruction sets

- Logic design

- Sequential Implementation • A simple, but not very fast processor design

## Pipelining

Get more things running simultaneously

### Pipelined Implementation

Make it work

# Coverage

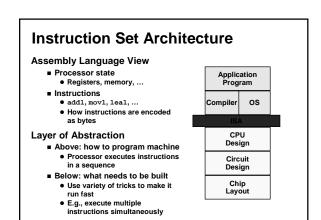

### The Approach

- Work through designs for particular instruction set

- Y86---a simplified version of the Intel IA32 (a.k.a. x86).

- If you know one, you more-or-less know them all

- Work at "microarchitectural" level

Assemble basic hardware blocks into overall processor

- structure

- » Memories, functional units, etc.

- Surround with control logic to make sure each instruction flows through properly

- Use simple hardware description language to describe control logic

- Can extend and modify

- Test via simulation

# Topics

- ∎Y86 ISA

- ■CISC vs. RISC

- ■High-level overview of MIPS ISA

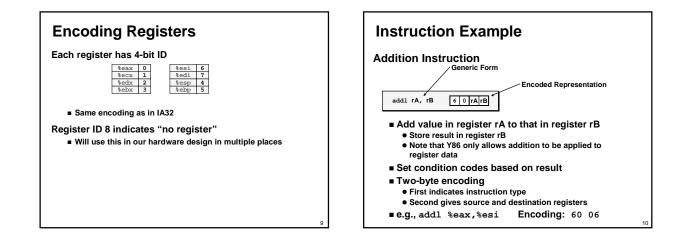

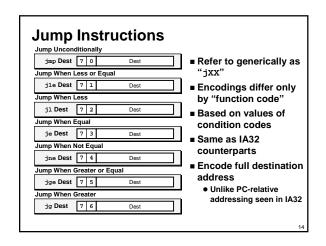

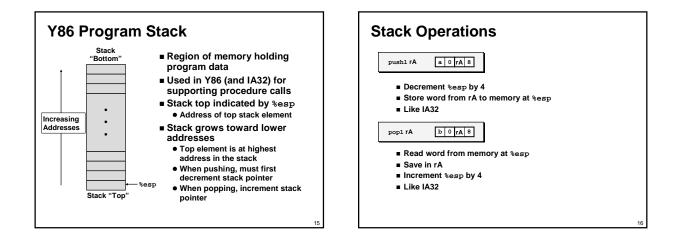

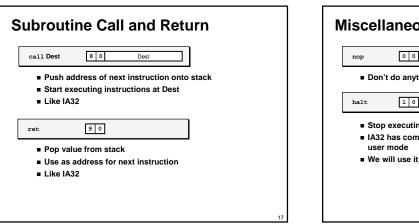

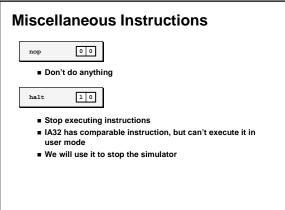

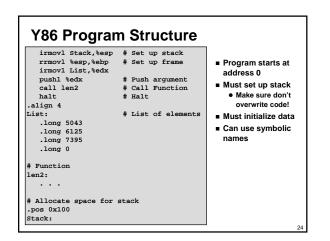

## **Y86 Instructions**

### Format

- 1--6 bytes of information read from memory

- Can determine instruction length from first byte

Not as many instruction types, and simpler encoding than with IA32

- Each accesses and modifies some part(s) of the program state

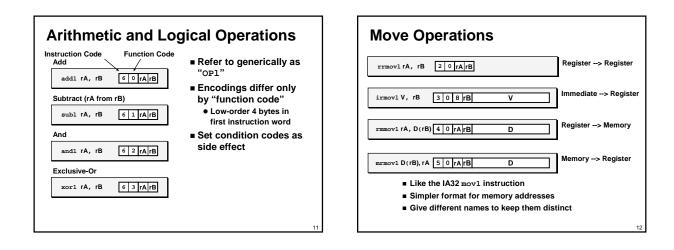

## **Move Instruction Examples**

| IA32     |         |              | Y86    |          |           | En | cod | ing |    |    |    |

|----------|---------|--------------|--------|----------|-----------|----|-----|-----|----|----|----|

| movl \$0 | xabcd   | , %edx       | irmovl | \$0xabcd | , %edx    | 30 | 82  | cđ  | ab | 00 | 00 |

| movl %e  | sp, %e  | abx          | rrmovl | %esp, %  | ebx       | 20 | 43  |     |    |    |    |

| movl -1  | .2(%ebj | p),%ecx      | mrmovl | -12(%eb  | p),%ecx   | 50 | 15  | £4  | ff | ff | ff |

| movl %e  | si,0x4  | lc(%esp)     | rmmovl | %esi,0x  | 41c(%esp) | 40 | 64  | 1c  | 04 | 00 | 00 |

|          |         |              |        |          |           |    |     |     |    |    |    |

| movl \$0 | xabcd   | , (%eax)     |        | —        |           |    |     |     |    |    |    |

| movl %e  | ax, 12  | 2(%eax,%edx) |        | -        |           |    |     |     |    |    |    |

| movl (%  | ebp,%e  | eax,4),%ecx  |        | -        |           |    |     |     |    |    |    |

|          |         |              |        |          |           |    |     |     |    |    |    |

|          |         |              |        |          |           |    |     |     |    |    |    |

|          |         |              |        |          |           |    |     |     |    |    |    |

|          |         |              |        |          |           |    |     |     |    |    |    |

|          |         |              |        |          |           |    |     |     |    |    |    |

|          |         |              |        |          |           |    |     |     |    |    |    |

|          |         |              |        |          |           |    |     |     |    |    |    |

| nix> yas eg. | .ys                |             |                              |

|--------------|--------------------|-------------|------------------------------|

| Generates    | "object code" fi   | e eg.yo     |                              |

|              | looks like disasse |             |                              |

| ,            |                    |             |                              |

| 0x000: 308   |                    |             |                              |

| 0x000: 308   |                    |             | Set up stack<br>Set up frame |

|              |                    | List,%edx # | set up frame                 |

| 0x00e: a02   |                    |             | Push argument                |

| 0x010: 802   |                    |             | Call Function                |

| 0x015: 10    | halt               |             | Halt                         |

| 0x018:       | ,align             |             | nure                         |

| 0x018:       | List:              |             | List of elements             |

| 0x018: b31   | .30000 .long       | 5043        |                              |

| 0x01c: ed1   |                    |             |                              |

|              |                    |             |                              |

| 0x020: e31   | .c0000 .long       |             |                              |

| unix> yis eg.yo                |                       |                                 |  |  |  |  |

|--------------------------------|-----------------------|---------------------------------|--|--|--|--|

| Instruction set simulator      |                       |                                 |  |  |  |  |

| <ul> <li>Computes e</li> </ul> | ffect of each instruc | tion on processor state         |  |  |  |  |

|                                | es in state from orig | •                               |  |  |  |  |

|                                |                       |                                 |  |  |  |  |

|                                |                       | Exception 'HLT', CC Z=1 S=0 O=0 |  |  |  |  |

| Changes to regi:<br>%eax:      | 0x00000000            | 0x0000003                       |  |  |  |  |

| secx:                          | 0x00000000            | 0x00000003                      |  |  |  |  |

| %edx:                          | 0×00000000            | 0x00000028                      |  |  |  |  |

| %esp:                          | 0x00000000            | 0x000000fc                      |  |  |  |  |

| %ebp:                          | 0x00000000            | 0x00000100                      |  |  |  |  |

| %esi:                          | 0x00000000            | 0x0000004                       |  |  |  |  |

| Changes to memor               | · · ·                 |                                 |  |  |  |  |

| 0x00f4:                        | 0x00000000            | 0x00000100                      |  |  |  |  |

| 0x00f8:                        | 0x00000000            | 0x0000015                       |  |  |  |  |

| 0x00fc:                        | 0×00000000            | 0x0000018                       |  |  |  |  |

### **CISC Instruction Sets**

- Complex Instruction Set Computer

- Dominant style through mid-80's

- Stack-oriented instruction set

- Use stack to pass arguments, save program counter

Explicit push and pop instructions

- Arithmetic instructions can access memory

- addl %eax, 12(%ebx,%ecx,4)

- requires memory read and write

Complex address calculation

### Condition codes

Set as side effect of arithmetic and logical instructions

#### Philosophy

Add instructions to perform "typical" programming tasks

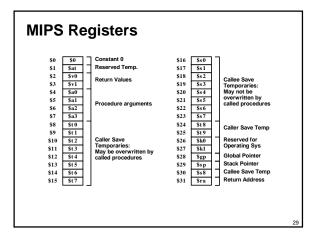

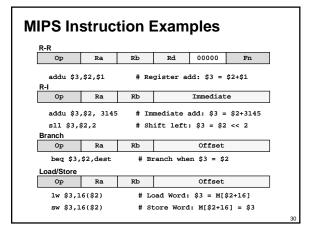

### **RISC Instruction Sets**

- Reduced Instruction Set Computer

- Internal project at IBM, later popularized by Hennessy (Stanford) and Patterson (Berkeley)

### Fewer, simpler instructions

- Might take more to get given task done

- Can execute them with small and fast hardware

### Register-oriented instruction set

- Many more (typically 32) registers

- Use for arguments, return pointer, temporaries

- Only load and store instructions can access memory

### Similar to Y86 mrmovl and rmmovl

- No Condition codes

- Test instructions return 0/1 in register

# **CISC vs. RISC**

#### **Original Debate**

- Strong opinions!

- CISC proponents---easy for compiler, fewer code bytes

- RISC proponents---better for optimizing compilers, can make

- run fast with simple chip design

### **Current Status**

- For desktop processors, choice of ISA not a technical issue

- With enough hardware, can make anything run fast

- Code compatibility more important

- For embedded processors, RISC makes sense Smaller, cheaper, less power

# Summary

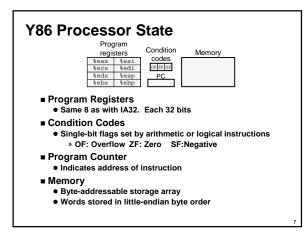

#### Y86 Instruction Set Architecture

- Similar state and instructions as IA32

- Simpler encodings

- Somewhere between CISC and RISC

### How Important is ISA Design?

- Less now than before

- With enough hardware, can make almost anything go fast

- Intel is moving away from IA32 Does not allow enough parallel execution

- Introduced IA64

- » 64-bit word sizes (overcome address space limitations)

- » Radically different style of instruction set with explicit parallelism

- » Requires sophisticated compilers